作为芯片制作的完整过程的最后一步,封装在电子供应链中看似有些不起眼,却一直发挥着极为关键的作用。作为处理器和主板之间的物理接口,封装为芯片的电信号和电源提供一个着陆区,尤其随着行业的进步和变化,先进封装的作用越来越凸显。而随着半导体工艺和芯片架构的日益复杂,传统SoC二维单芯片思路已逐渐行不通,chiplet多个小芯片封装成为大势所趋。所以,若想延续摩尔定律的寿命,唯有解开后端“封装”技术瓶颈,部署重兵在此领域。最近,业界又对高级MCP设计一致看好,并计划将急剧加速其发展。

英特尔虽然在10 nm工艺技术上延迟了4 年,导致全球芯片制造的龙头宝座拱手让给台积电,但从 2019 年开始,英特尔展开了绝地大反攻,这一战就是从封装开始。此前,英特尔已公布六大技术支柱,制程&封装正是其中最底层的支柱,封装正成为产品创新的催化剂。

近日,英特尔在上海召开发布会,分享了3项重大封装的全新技术架构,强调能同时提供2D 和 3D 封装技术。

英特尔公司集团副总裁兼封装测试技术开发部门总经理BabakSabi强调:英特尔是一家垂直集成的IDM厂商,具备六大技术优势当中的全部领域的专门技术细节。这也给英特尔提供了无与伦比的优势,从晶体管再到整体系统层面的集成,英特尔可提供全面的解决方案。而在在异构集成时代,作为IDM的英特尔,对于开发方案关注的又非常全面。英特尔希望所有的产品都可以很轻松地集成在客户的平台上。

BabakSabi介绍了英特尔封装测试的全流程。一般来说,芯片的封装测试会经历以下几个步骤:

已知合格芯片(KGD),连接到裸片上的具体接口以及插口,通过这种方法来对裸片来测试,确保提交给客户所有的芯片都是质量合格的;

统一测试,对完成封装的芯片以及基板进行统一的测试,确保它们能正常运作;

英特尔对多芯片封装架构(MCP)投入了大量的时间进行研究。英特尔院士兼技术开发部联合总监Ravi Mahajan阐述了他们对于MCP的愿景:希望把多个功能集成在封装内实现芯片和小芯片的连接,同时也能够在一定程度上帮助整体芯片实现单晶片系统和片上系统(SOC)的功能。所以,低功耗高带宽的高密度互连对于实现这个愿望至关重要。Mahajan解释,为做到这一点:

对于传递信号来讲,它是在整个半导体及芯片表面来进行传递,从而会受到金属表面粗糙度影响,而随着整个信号的传递它可能会受到损耗。英特尔专门的制造技术会让金属表面粗糙度得到大幅度降低。同时采用全新的布线方法,让其间的串扰变得更少。除此之外英特尔也采用全新空隙布线生产的基本工艺和流程,可以越来越好的通过电介质堆栈设计进一步减少两者之间信号传导的损耗。

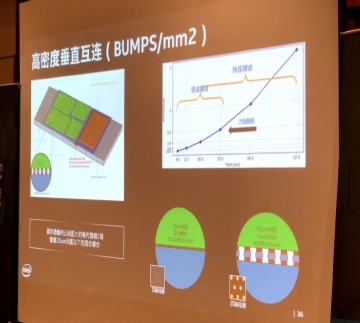

此外,对于高密度,高带宽互连这一技术,Ravi Mahajan指出它分为两个裸片叠在一起的3D互连和两个裸片进行水平的连接的2D互连。对于3D互连而言,导线数量比较少,速度比较快,另一种恰恰相反。对比串行和并行两种传输方式,并行将会大幅度降低延迟,还能更好地改善其速度。加上良好的设计,还可以把整个能耗降低大概10个百分比。为做到这一点,就必须要有先进的封装技术进行配合,这也是为什么英特尔开发封装技术的重要原因。

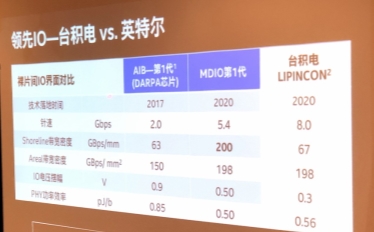

基于高级接口总线(AIB)物理层互连技术,Intel发布了这种名为MDIO的全新裸片间接口技术。MDIO技术上的支持对小芯片IP模块库的模块化系统模块设计,能效更高,响应速度和带宽密度可以是AIB技术的两倍以上。Mahajan强调,这些全新封装技术将与Intel的制程工艺相结合,成为芯片架构师的创意调色板,自由设计创新产品。

据了解,MDIO是一种性能更好的芯片到芯片之间的接口(引脚)技术。相对于之前英特尔所使用的AIB(高级接口总线)技术,MDIO能够在更小的连接面积内实现更高的数据带宽。这样,即便是使用ODI技术中更细的针脚也能够很好的满足芯片之间数据带宽的需求。

通过在连接方式、连接层、连接引脚等影响芯片堆叠的细节上的全面技术革新,英特尔终于实现了在单一基板上以水平和垂直方式封装更多芯片(Die)的愿景。

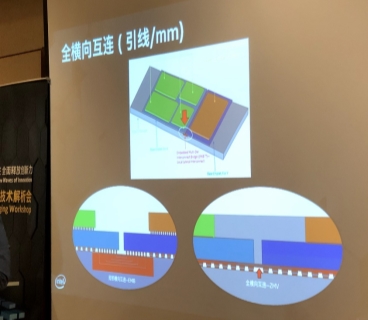

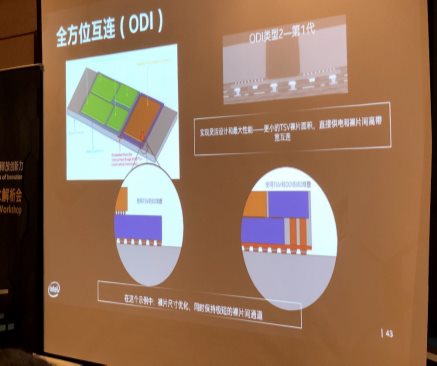

为了进一步提升水平与垂直堆叠的灵活性,英特尔还推出了一个额外的物理互连层技术——ODI。此技术为封装中小芯片之间的全方位互连通信提供了更大的灵活性。ODI存在于基板与芯片之间,在这一层上,英特尔能够最终靠远大于传统封装技术的密度来进行埋线和布置连接针脚。从而在保证芯片供电的情况下实现更高的互联带宽。

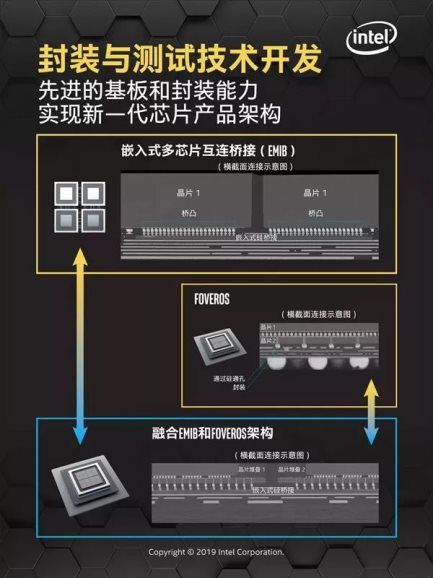

提到2D芯片封装以及裸片之间的互连,我们一般考虑的是怎么样才能做到多薄,其次是几个裸片之间的间距问题。对于传统的有机封装加上先进的制造技术能把每平方毫米的导线。而英特尔的EMIB(嵌入式多芯片互连桥接)技术能实现更好的导线密度。Mahajan介绍,嵌入式多管芯互连桥(EMIB)是用一小块硅在MCP中的两个管芯的相邻边缘之间提供自由的互连性。EMIB目前集成了四个金属化平面--2个信号和2个电源/地(主要用于屏蔽,但也可用于芯片之间的P / G分配)。

Mahajan提供了有关EMIB的其他技术信息。他指出EMIB平面的金属厚度介于硅片RDL层和封装迹线之间,实现了互连间距和损耗特性之间的平衡。“我们现在是2um的线um线um 线um线间距努力。我们对EMIB的Si分析表明,长达8mm的长度仍能提供足够的眼图余量。从概念上讲,EMIB可以达到~200平方毫米。”(例如,相邻芯片边缘之间的距离为25 mm,宽度为8 mm)。

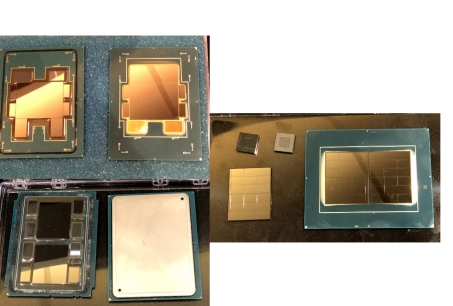

3D 封装技术可以将产品分解成更小的“小芯片”,其中的电源传输电路、SRAM、I/O元件可以建入底层的基础芯片(basedie)当中,而高效能逻辑芯片则堆叠在上面,同时Foveros也具备在新的装置设计中混搭各种硅知识产权模组、各种存储、I/O元件的弹性。

Foveros技术对于产业来说最迷人的地方在于他可以将过去漫长的重新设计、测试、流片过程统统省去,直接将不同厂牌、不同IP、不同工艺的各种成熟方案封装在一起,从而大幅降低成本并提升产品上市速度。同时,这种整合程度的提升也能够进一步缩小整体方案的体积,为万事万物的智能化、物联网化打开全新的大门。

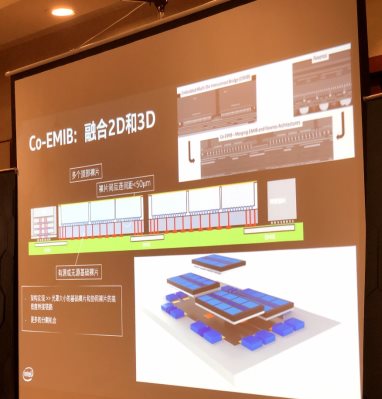

利用利用高密度的互连技术,将EMIB(嵌入式多芯片互连桥接) 2D封装和Foveros3D封装技术结合在一起,诞生了Co-EMIB,它可实现高带宽、低功耗,以及相当有竞争力的I/O密度。Co-EMIB能连接更高的计算性能和能力,让两个或多个Foveros元件互连从而基本达到SoC性能,还能以非常高的带宽和非常低的功耗连接模拟器、内存和其他模块。

Mahajan总结到,整个业界都在不断推动先进多芯片封装架构的发展,更好的满足高带宽、低功耗的需求。而英特尔拥有多项关键基础技术,包括EMIB、Foveros还有Co-EMIB等,这些都是MCP高密度实现的关键。英特尔并不仅仅是有物理层的技术,还有先进的IO技术和高密度的封装技术这些都可以进行协同设计。

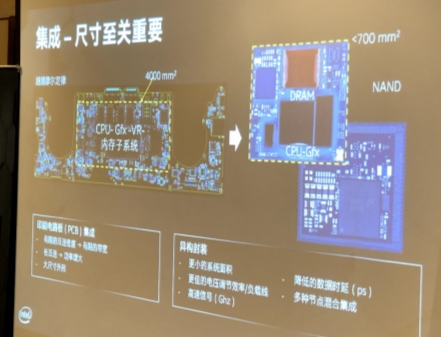

对于封装互连技术主要有两种方式:一是把主要的相关功能在封装上进行集成。其中一个就是把电压的调节单元从母板上移到封装上,通过这种方式实现全面集成的电压调节封装。另外一种则是为SOC片上系统分解的方式,把具备不同功能属性的小芯片来进行连接,并放在同一封装里,通过这种方法我们能轻松实现接近于单晶片的特点性能和功能。

来自英特尔封装研究事业部组件研究部首席工程师AdelElsherbini解释:不管是选择哪一种的实现路径,都需要我们做到异构集成和专门的带宽需求,而异构集成和专门的带宽需求也可以帮助我们去实现密度更高的多芯片集成。

1.用于堆叠裸片的高密度垂直互连,可以大幅度的提高带宽,同时也可以实现高密度的裸片叠加。

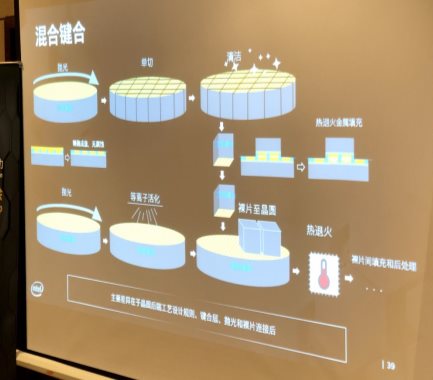

AdelElsherbini介绍,通过高密度互连技术,除了可以实现高带宽和低延迟之外,还会带来更多的优势。随着芯片尺寸越来越小,每平方毫米的导线接头将会越来越密,为了保证带宽,晶体管的间距就会变得越来越短,而传统焊料技术已接近极限,为此一种全新的技术诞生了——混合键合。此技术能让芯片之间的间距达到10微米,桥凸和互连密度上也会做的更好。

英特尔希望在整个封装层面都可以实现小芯片互连,作为横向互连技术,其中需要考虑的就是直线间距。随着直线间距越来越短,在同样面积下可以安装更多硅片,同时信号之间的传导距离也会越来越短。使用有机中介层是更好的方案,因为它比硅的成本更低。但是,用有机中介层有一个缺点,就是必须要进行激光钻孔,通过光刻定义的通孔使得导线和通孔的宽度一致,这样就不需要焊盘进行连接,这样就可以在不牺牲传导速度的情况下而做到。

ODI技术可以让上下方的基础裸片的带宽速度保持很快;此外,让上方的小芯片在不需要中间通孔情况下,可直接获得封装的供电;较传统技术而言,使得基础裸片比上方搭载小芯片的面积总和更大。通过这一种并排互连的形式,可以让延迟下降2.5倍,功耗缩短15%,带宽上提高3倍。

无论是高密度度垂直互连、全横向互连还是全方位互连,这三种互连方式都能大大的提升每立方毫米上的功能并实现类似于单晶片的性能。

英特尔围绕自身在半导体技术和相关应用方面的能力构建了支撑自身“以数据为中心”战略的六大技术支柱,来应对未来数据量的爆炸式增长、数据的多样化以及解决方法的多样性的挑战。

而半导体晶片堆叠技术的出现则让英特尔看到了新方向。通过将不同功能、不同IP的晶片封装在一起,数据中心在未来有望大幅度简化架构,将计算类型的分裂严格限制在芯片内部,从而在更大的层面上实现统一。这就完美解决了计算架构分裂所带来的管理及运维挑战。但是,3D堆叠技术依旧存在诸多难点,在将来就要看英特尔在这场持续投入的马拉松中如何运筹帷幄了。

随着新的多核Intel Atom x6000E系列处理器的问世,Avnet Integrated正在扩展其基于Intel Atom、Intel Pentium、Celeron N和J系列处理器的标准模块系列。Avnet Integrated已将新的Intel Atom x6000E系列处理器整合到所有四种既定的嵌入式标准COM Express中 6型和10型,SMARC 2.1 和Qseven 2.1. 随着现成的嵌入式模块和合适的设计工具的可用性,新处理器技术在开发创新应用程序的早期阶段就可用了。 新的Intel Atom x6000E系列处理器基于10nm工艺技术,代号为“Elkhart Lake”,与具有相同CPU核数

嵌入式计算模块 /

全球最大芯片厂商英特尔公司深陷“芯片门”丑闻,芯片漏洞问题持续发酵。据美国新闻媒体报道,英特尔在美国面临至少三起来自消费者的集体诉讼,公司首席执行官布赖恩·克尔扎尼奇被曝去年大幅减持公司股票,不过英特尔否认此事与芯片漏洞存在关联。 美国石英财经网站等媒体日前披露,英特尔公司芯片存在严重技术缺陷,引发全球用户对信息安全的担忧。专业技术人员指出,英特尔芯片缺陷导致的漏洞可能会影响几乎所有电脑和移动电子设备用户的个人信息安全,受波及设备数以亿计,漏洞的修补过程可能会引起全球个人电脑性能显而易见地下降。 据美国“小发明网站”报道,英特尔面临的三起集体诉讼分别发生在美国加利福尼亚州、俄勒冈州和印第安纳州。诉讼者均指控英特尔数月前就了解芯片存在漏洞,却未及时对外公

当前,5G、人工智能、无人驾驶等技术加快速度进行发展,应用场景也愈加广泛,这背后,有着灵活高效、高性能、低功耗等优势的可编程芯片FPGA功不可没。随着应用场景的扩大,FPGA的市场规模也迎来迅速增加。IDC预计,全球传统FPGA市场规模将在2024年达到71.55亿美元。作为FPGA高需求国家之一,中国FPGA应用市场的发展被广泛看好,这也代表着我们需要更多FPGA人才,来满足日渐增长的市场需求,助力科学技术事业发展。 近日,由英特尔FPGA中国创新中心和英特尔FPGA大学计划联合发起的 第一届“芯云未来——‘FPGA菁英挑战赛’高校进行时”(以下简称:菁英挑战赛)真正开始启动 , 面向 在校大学生进行FPGA基础知识普及和行业推广,帮助学生

FPGA中国创新中心的创新人才培养之道 /

据外媒报道,英特尔旗下子公司Mobileye在拉斯维加斯举行的2019年国际消费电子展(CES)上透露了大量信息,包括与法雷奥(Valeo)合作,为两家中国公司提供实现真正无人驾驶公共交通工具的平台,以及与英国国家测绘局(Ordnance Survey)合作地图测绘项目。此外,该公司还推出了自动预防制动(APB)系统,该系统是自动紧急制动系统的增强版,可使用公式来确定汽车何时会发生危险状况。并且在潜在危险发生时,可通过让汽车减速、逐渐停止,来防止发生碰撞事故。 Mobileye公司首席执行官Amnon Shashua解释道:“APB通过采用几乎不会让人注意的预防性制动而不是突然制动,帮助车辆恢复到更安全的位置,从而防止碰撞事故发生

9月30日消息,据外电报道,诺基亚计划在一种平板电脑式设备中使用英特尔芯片。这种设备将使用WIMAX技术进行通讯。诺基亚和英特尔已经同意联合来测试,以保证英特尔WIMAX芯片兼容诺基亚的便携式设备和网络设备。 XIMAX是一种能够以宽带网的速度无线传输数据的技术。英特尔一直是WIMAX技术的领先者。 诺基亚目前还没用任何英特尔的芯片。诺基亚计划2008年在诺基亚N系列互联网平板电脑中使用英特尔代号为“Baxter Peak”的芯片。 诺基亚希望提供能够在Sprint Nextel公司建设的WIMAX网络中使用的技术。

日前,英特尔公司宣布将投资10亿-15亿美元,更换新墨西哥州一工厂的设备,该厂将于2008下半年开始制造先进的45纳米晶体管产品。其发言人说,英特尔对2007年53亿-57亿美元的资本支出预测中,已经包含了今年要花的设备更新支出。 这已经是英特尔筹建的第四做45纳米工厂。据可靠消息,最迟在今年下半年,英特尔将启用更为先进的45纳米制程,推出第三代Core微架构处理器与原生型四核心处理器(代号:Yorkfield)。400颗45纳米晶体管可放置在相当于人类红血球那么小的东西之上。 不过,据目前的迹象看,一切比英特尔预想的还要快。毋庸置疑,45纳米技术已渐行渐近,最快有可能是在数月后量产。 能确定的是,英特尔肯定不满足在未来十

英特尔(Intel)公布去年第4季以及2016年财报,整体营运小幅优于市场预期,但由于PC市场需求持续衰退,PC有关部门出货量出现衰退,而公司虽因推出高阶产品,使得ASP出现上扬,加上合并Altera,因此表现优于市场表现;分析师指出,预估英业达(2356)将受惠。 Intel去年第4季营收164亿美元,年增10%,优于公司预期,毛利率61.7%、也小幅优于公司预期,税后纯益36亿美元、年减1%,每股获利(EPS)0.73美元,整体状况小幅优于市场预期。 Intel预估今年第1季营收143亿~153亿美元,季减12.8%~6.7% 之间,主因淡季因素而出现下滑,但就整体预估而言,仍偏保守,EPS预估在0.51美元~0.61美元

据国外新闻媒体报道,Nvidia CEO黄仁勋(Jen-Hsun Huang)日前在接受媒体采访时表示,英特尔AtomCPU性能太弱,无法运行当前的大型主流软件,最终只能破坏软件产业。 黄仁勋称:“基于Atom处理器的上网本无法运行当前的主流应用,如EA、Adobe和微软的软件。我这里提到的都是全球最大的软件公司,而Atom处理器对他们的应用却无能为力,最终只能是破坏软件产业。” 关于“英特尔要求Atom处理器用户使用英特尔芯片组”的说法,黄仁勋说:“我听到过这种观点,但我对此置之不理,因为我不理解英特尔这种做法,为何需要限制伟大的PC进入市场?我希望英特尔不要阻止用户获得最具创新性的产品。” 英特尔与Nvidia

学习OpenCV 3(中文版) ([美] 安德里安·凯勒,[美] 加里·布拉德斯)

直播回放: 英特尔 FPGA 可编程加速平台介绍,走近 AI、数据中心、基因工程等大咖工程

根据CounterpointResearch的最新报告,2023年第4季度全世界代工产值相比上一季度增长了约10%。这主要是由于智能手机和个人电脑行业供应链库存 ...

X-Silicon日前展示了其开放标准、低功耗 C-GPU 架构,将 GPU 加速与 RISC-V 矢量 CPU 内核和紧密耦合的内存相结合,形成低功耗、单 ...

台湾清华大学半导体研究学院院长暨台积电前副总裁林本坚,昨日在日本东京进行专题演讲时提到,浸润式微影和极紫外光微影技术,是量产个位数 ...

4 月 3 日消息,芯片巨头英特尔公司今天公布了其晶圆代工业务部门的详情信息,作为其财务报告格式变更的一部分,该部门现在作为一个独立 ...

4 月 2 日消息,根据经济日报报道,台积电美国亚利桑那州工厂正处于“冲刺”状态,计划 4 月中旬进行首条生产线试产,如果一切顺利, ...

CMF120650.5OHMS0.1%50PPMTAPE&REEL330MM

Digi-Key KOL视频来袭~欢迎进入MicroPython的奇妙世界

有奖直播【Keysight World Tech Day 2023分论坛——汽车无人驾驶与新能源】

站点相关:市场动态半导体生产材料技术封装测试工艺设备光伏产业平板显示EDA与IP电子制造视频教程

- 上一篇: 一文了解英特尔CPU接口的发展史

- 下一篇: 招商引资 嘉兴有戏

热线电话:

热线电话: